# 53A-412 PROGRAMMABLE DIGITAL I/0 CARD OPERATING MANUAL

© Copyright 1991 by Colorado Data Systems, Inc. A Subsidiary of Tektronix Englewood, CO 80110 All rights reserved.

Printed in U.S.A.

#### WARRANTY

Colorado Data Systems, Inc. (CDS) products (hardware and firmware) are warranted against defects in materials and workmanship, and are warranted to meet the performance specifications as listed in the current catalog and/or data sheet for the specific product being warranted. This warranty applies for three (3) years following the date of shipment. CDS will, at its option, repair or replace, at no cost to the customer, products which prove to be defective during the warranty period, provided the defect or failure is not due to misuse or abuse of the product. The customer is responsible for shipment of the defective product to the CDS factory. Software products are supplied on a site license basis subject to the same performance warranty provisions; the materials and distribution provision applies to the distribution media only. NO OTHER WARRANTY IS EXPRESSED OR IMPLIED, INCLUDING WARRANTY FOR FITNESS OF PURPOSE. CDS SHALL, IN NO CASE, BE LIABLE FOR CONSEQUENTIAL DAMAGES.

# TRADEMARK NOTIFICATION

GW BASIC is a registered trademark of the Microsoft Corp.

IBM and PC are registered trademarks of the IBM Corporation.

All other brand and product names are trademarks or registered trademarks of their respective companies.

# 53A-412 PROGRAMMABLE DIGITAL I/0 CARD OPERATING MANUAL

| DESCRIPTION                          | 1  |

|--------------------------------------|----|

| CONTROLS AND INDICATORS              |    |

| Address Select Switch                | 4  |

| Power LED                            | 4  |

| Fuses                                | 4  |

| Function LEDs and Switches           | 4  |

| Punction Leds and Switches           | 6  |

| Built-In Test Equipment              | 6  |

| External Handshake Controls          | Ü  |

| SPECIFICATIONS                       | 8  |

| OPERATION                            |    |

| Overview                             | 11 |

| Command Protocol And Syntax          | 11 |

| Command Summary                      | 12 |

| Command Descriptions                 | 14 |

| INSTALLATION                         | 48 |

| APPENDIX A                           |    |

| 53/63 SERIES SYSTEM COMMANDS         | 49 |

| APPENDIX B                           |    |

| INPUT/OUTPUT CONNECTIONS             | 50 |

| APPENDIX C                           |    |

| SAMPLE BASIC PROGRAM FOR THE 53A-412 | 52 |

| APPENDIX D                           |    |

| OPTIONS                              | 59 |

# 53A-412 PROGRAMMABLE DIGITAL I/O CARD

# **DESCRIPTION**

The 53A-412 Programmable Digital I/O Card is a printed circuit board assembly for use in a CDS 53/63 Series System. The 53A-412 provides 48 TTL and CMOS compatible, bidirectional digital I/O lines. For programming convenience, and to help in defining proper test flow, these 48 programmable I/O signal lines are organized as six 8-bit bytes. Two available options further extend the usefullness of the Card by adding optical isolation or open collector capability to the I/O.

Each of the six bytes can be completely and independently configured under full program control. All commands and responses are normally in ASCII hex notation for ease of programming, and to insure compatibility with the widest range of systems controllers. However, a binary capability is also supplied standard for those applications requiring increased data transfer speed. Programmable parameters include:

- o selection of any byte as either input or output

- o definition of masks for input and output data

- o I/O control on command basis, on external handshake, or on a programmable time count

- o logic sense of input, output and handshake lines

- o full reporting of operating parameters at any time

Data output can be controlled as bits, as individual bytes, and/or as groups of bytes. Control of the output be directly applied on a command basis, or further qualified and controlled by using external handshakes, or by means of a programmable time count.

Data input is also fully under program control. The card can report the state of all input bytes, groups of input and/or output bytes, and single bits of a byte. Input data can be updated on a command request basis, or on a qualified basis using external handshakes.

User-defined masks can be overlaid on the data prior to output. Masks may also be applied to individual input bytes before they are returned to the system controller to improve data post-processing speed and to promote ease of data interpretation.

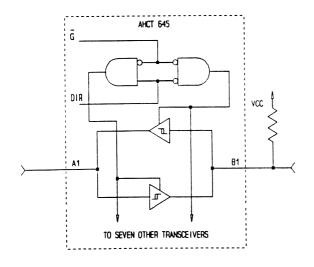

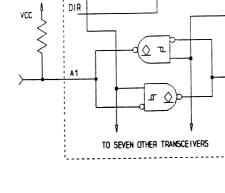

The sense of inputs and outputs can be set to either active high or active low under program control. The active edge can also be programmed for handshake lines. All I/O lines are both TTL and CMOS compatible, with up to 24 mA of sink current provided for each output. With Option 01 installed, the I/O section of the card is fully isolated from system ground using optoisolators and an isolated power supply contained on the card.

External (handshake) control signals are provided for output and input data control. Output data control signals are Ready For Data (RFD), Data Available (DAV), and External Tri-State control (ETSO - ETS5). Input data control signals are Data Ready (DRD) and Data Acknowledge (DAK).

A binary I/O mode is provided which allows a total of 6000 bytes to be allocated for buffered binary I/O through the card. Two modes are provided for binary input: Mode 1 inputs data

as long as there is free memory in the buffer to accept it, while Mode 2 overwrites the oldest data in memory when the input buffer is filled. Binary input is controlled by the Data Ready handshake. Data can be simultaneously read from the input buffer while new data is being strobed in, dynamically freeing memory for additional input. The card can also be programmed to generate an interrupt when the input buffer is full.

Binary output can be controlled by either the Ready For Data handshake or on a programmable time basis from 100 µs to 858 seconds. Two modes are provided: mode 1 outputs data as long as there is data in the output buffer. Mode 2 allows pre-loading the output buffer, then defining a 'thread' sequence to control how preloaded data is output. For mode 1, data can simultaneously be loaded into the card while data is being output. The number of bytes left to be output can be read at any time, and the card programmed to generate an interrupt when the output buffer is empty. For mode 2, an interrupt can be programmed to occur when a breakpoint occurs in the sequence.

The 53A-412 provides full access to system status information, which is especially helpful during system trouble-shooting, software de-bugging, and operational system checks. At any time, the system controller can read the state of the external handshake lines, the programmed I/O configuration, the programmed active edges of all handshake signals, which handshake signals are active, the programmed logic sense of each I/O byte, the tri-state condition of each output byte, and up-to-date error data.

#### BITE

Built-in-Test-Equipment (BITE) is provided on the card by an internal loop-back path that allows the card to be tested with its outputs tri-stated, verifying I/O paths for each byte. A self test is automatically performed on power up, or it can also be commanded. Front panel LEDs indicate the error status, data handshake signals, current tri-state conditions, input/output configuration, and individual I/O bits. In addition, the Query and Operation commands can be used to determine the current state of the card during operation.

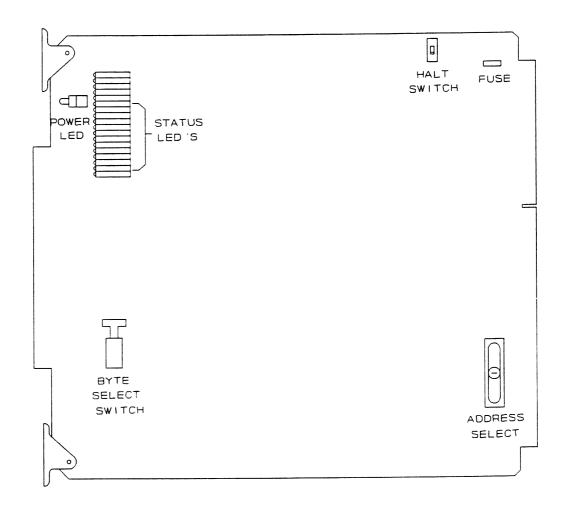

Figure 412-1: 53A-412 Controls and Indicators

#### CONTROLS AND INDICATORS

The following controls and indicators are provided to select and display the functions of the 53A-412 Card's operating environment. See Figure 412-1 for their physical locations.

# Address Select Switch

The 53A-412 Card has a miniature 10-position switch which selects the card's address (0-9) in the 53/63 Series System. Open the switch's cover and use a screwdriver with a narrow, flat blade to turn the cam-action wiper to the desired position.

### Power LED

The Power LED provides a valuable diagnostic tool by giving the system programmer a visual indication of the action which the system is currently taking. Whenever the 53A-412 Card is addressed by the system controller, the Power LED goes out. The LED remains out until another function card is addressed. Since only one function card can be addressed at a time, an unlit Power LED indicates the function card with which the system controller is currently communicating. The Power LED being lit not only indicates that the 53A-412 Card is unaddressed, but that all required dc power (5V dc) is being supplied.

# **Fuses**

The 53A-412 Card has a single +5V fuse. The fuse protects the card in case of an accidental shorting of the power bus or any other situation where excessive current might be drawn.

If the +5 V fuse blows, remove the fault <u>before</u> replacing the fuse. Replacement fuse information is given in the <u>Specifications</u> section of this manual. Figure 412-1 shows the location of this fuse on the 53A-412 Card.

# Function LEDs and Switches

# LEDs

The following LEDs are provided at the top front edge of the 53A-412 Card to indicate the status of the card's operation:

# ERR

Indicates a programming error has occurred. This LED will remain lit until the error condition is cleared.

#### **RFD**

Indicates the state of the Ready for Data handshake signal. This LED lights when the external device strobes ready for data indicating it is ready for more data. It is cleared when new data is output by the card.

# DAV

Indicates the level of the Data Available handshake signal. This LED lights when the DAV line is low. It clears when the DAV line goes high.

# DRD

Indicates the state of the Data Ready handshake signal. This LED lights when the external device strobes data ready indicating new input data is valid. It is cleared when the controller reads the input data.

# DAK

Indicates the level of the Data Acknowledge handshake signal. This LED lights when the DAK line is low. It is cleared when the DAK line is high.

# BYTE (B50, B51, B52)

Three LEDs that indicate in binary which of the six bytes (0 through 5) the bit LEDs (D7-D0 LEDs) are currently displaying, as follows:

| Byte            | LEC        | ) status:  |            |

|-----------------|------------|------------|------------|

| <u>Selected</u> | <u>B52</u> | <u>851</u> | <u>850</u> |

| 0               | unlit      | unlit      | unlit      |

| 1               | unlit      | unlit      | lit        |

| 2               | unlit      | lit        | unlit      |

| 3               | unlit      | lit        | lit        |

| 4               | lit        | unlit      | unlit      |

| 5               | lit        | unlit      | lit        |

| *6              | lit        | lit        | unlit      |

| *7              | lit        | lit        | lit        |

<sup>\*</sup> Bytes 6 and 7 are unused.

#### I/O

Indicates the programmed input/output state of the current byte being displayed. The LED is lit if the byte is programmed as an output, and unlit if programmed as an input byte.

# TRI

Indicates the tri-state condition of the byte currently being displayed. A lit LED indicates the byte is tri-stated.

# D7 - D0

Indicates the state of each bit of the currently displayed byte. The LED being lit indicates the bit is high (TTL logic '1'). An unlit LED indicates the bit is low (TTL logic '0'). D7 is the most significant bit, and D0 the least significant bit. Bytes 6 and 7 are unused, and will light all the data bit LEDs.

# Switches

The following switches are provided to select the proper functions for the 53A-412 Card's operating environment:

# Halt Switch

This two-position slide switch is located near the card's backplane edge connector. It selects the state of the 53A-412 Card after an @XH (Halt) or STOP command is received by the 53/63 Series System.

a. If the Halt switch is in the ON position, then the 53A-412 Card is reset to its power-up state, all parameters are reset to their default values, and the Power LED is lit.

b. If the Halt switch is in the OFF position, then the 53A-412 Card becomes unaddressed, the Power LED is lit, and any programmed parameters of the card remain unchanged.

# Byte Select Switch

The Byte Select switch located on the lower left is a momentary action switch that controls which of the six I/O bytes is currently being displayed on the LEDs. Each time the switch is depressed, the state of the next byte in sequence is displayed on the LEDs. For example, if the state of byte 0 is currently displayed, the state of byte 1 will be displayed after the switch is depressed. The BYTE LEDs will display the number of the selected byte (see BYTE in the listing of LEDs).

# Built-In Test Equipment

BITE (Built-In Test Equipment) is provided on the card by an internal loop-back path, which allows the card to be tested with the outputs tri-stated. The self test automatically tests and verifies all loop-back paths for each byte.

Self test is automatically performed on power up, and can also be commanded. All the outputs are checked with their corresponding inputs, and with the output drivers in tri-state.

Front panel LEDs indicate the status of various system operating parameters. In addition, the Query and Operation commands can be used to determine the current state of the card during operation, including error codes (see the Query command in the <u>Command Descriptions</u> subsection).

# External Handshake Controls

# Output Data

# Ready For Data (RFD)

Ready For Data is an input from an external device indicating it is ready for data. This signal is programmable to be either positive or negative edge triggered true.

#### Data Available (DAV)

Data Available is an output to an external device indicating valid data is available on the outputs. This signal is programmable to be either positive or negative edge triggered true.

# External Tri-State control (ETSO - ETS5)

Six external tri-state control lines are provided, one for each of the six bytes. These lines are inputs from an external device which cause the corresponding byte to go into tri-state (high impedance). The tri-state control lines are programmable to be either active high or active low.

# Input Data

# Data Ready (DRD)

Data ready is an input from an external device indicating valid data is at the inputs. This signal is programmable to be either positive or negative edge triggered true.

# Data Acknowledge (DAK)

Data acknowledge is an output to an external device indicating the input data has been accepted. This signal is programmable to be either positive or negative edge triggered true.

# **SPECIFICATIONS**

Number of I/O Channels: 48.

Configuration: I/O lines selectable as input or output on an 8-bit byte basis.

Also tri-state programmable on an 8-bit byte basis.

Byte Transfer Polarity: All input and output bytes individually selectable as active

high or active low.

Input Data: Returned as two hexadecimal ASCII characters per byte, or in

binary.

Input Control: On program command or with external Data Ready and Data

Acknowledge handshake.

Output Data: Programmed as two hexadecimal ASCII characters per byte, or

on an individual bit basis, or in binary.

Output Control: On program command, with external Ready for Data and Data

Available handshake, or on a programmable time count.

Tri-State Control: On program command on an individual byte, and by individual

external tri-state control signals for each byte.

Mask Capability: On an individual byte basis, for input or output. AND, OR,

and XOR (exclusive OR) masking provided.

Byte Ordering: A predefined sequence for input or output byte transfer may

be programmed. Bytes may be transferred in any required

order.

Interrupt Modes: Program selectable, on Ready For Data handshake, Data Ready

handshake, Binary Input Buffer Full, Binary Output Buffer

Empty.

External Control

Logic Sense: Data Available, Ready For Data, Data Acknowledge, and Data

Ready control line polarities are all individually program

selectable as low or high true.

I/O Signal Type: TTL and CMOS compatible (74AHCT245 driver). Option 02

provides TTL open collector outputs (74LS641).

D.C. Electrical

Characteristics: -10° to +55° C., typical specs at 25° C. A minus sign indicates

current flowing out of the card.

<u>Isolation Resistance</u>: (Option 01 only) > 100e6 ohms at 500V dc.

Isolation Voltage: (Option 01 only) > 250V dc.

| <u>min</u> | typ | <u>max</u>                          | <u>units</u>                                                  |

|------------|-----|-------------------------------------|---------------------------------------------------------------|

|            |     |                                     |                                                               |

| 4.4        | 5.0 |                                     | V                                                             |

| 3.84       | 4.2 |                                     | V                                                             |

|            |     |                                     |                                                               |

|            | 0   | 0.1                                 | ٧                                                             |

|            | 0   | 0.5                                 | V                                                             |

|            | · · | 24                                  | mΑ                                                            |

| 2.0        |     |                                     | ٧                                                             |

| 2.0        |     | 0.8                                 | v                                                             |

|            |     |                                     | · .                                                           |

|            |     |                                     | μA<br>μA                                                      |

|            | 4.4 | 4.4<br>3.84<br>5.0<br>4.2<br>0<br>0 | 4.4 5.0<br>3.84 4.2<br>0 0.1<br>0 0.5<br>24<br>2.0 0.8<br>230 |

There are 22K pull-up resistors to +5V on all I/O and handshake lines to account for floating inputs. The input IC uses 1.0  $\mu$ A max, while the pull-down resistors require 5V / 22K = 227.6  $\mu$ A.

# External Control Lines:

External Tri-state Input to Tri-state Active: Typical: 30 nS.

Maximum: 63 nS.

Valid Output Data to

Data Available Strobe: 0 nS.

Data Acknowledge to Data

Ready Strobe Delay: 0 nS.

Maximum Output Data Rate:

Buffered binary data using either the internal trigger or the

RFD handshake:

10 KHz (1 to 3 output bytes) 8 KHz (4 to 6 output bytes)

ASCII hex data: 8 KHz.

Maximum Input Data Rate: Buffered binary data using the DRD handshake: 5 KHz.

Power Requirements: All required dc power is provided by the internal power supply

in the 53/63 Series Card Cage.

Voltage

(5-volt Supply): 4.75 V dc to 5.25 V dc.

Current 1.10 A, maximum quiescent.

(5-volt Supply): 3.2 A, peak.

With Opt. 01: 1.7 A, maximum quiescent.

3.8 A, peak.

Power-up Defaults: All I/O pins tri-stated.

All bytes defined as inputs, active high. All external handshake lines disabled.

Interrupts disabled.

Fuses: Replacement fuse: CDS P/N 42202-52001 (4 or 5 amp).

Cooling: Less than 10°C temperature rise with 1.2 liters/sec. of air at a

pressure drop of 0.03 mm of H<sub>2</sub>O.

Temperature: 0°C to +50°C, operating.

-40°C to +85°C, storage.

Humidity: Less than 95% R.H. non-condensing, 0°C to +30°C.

Less than 75% R.H. non-condensing, +31°C to +40°C. Less than 45% R.H. non-condensing, +41°C to +50°C.

<u>Dimensions</u>: 197 mm x 221 mm x 19 mm (7.75 in x 8.69 in x 0.5 in)

<u>Dimensions</u>, Shipping: When ordered with a CDS card cage, this card will be installed

and secured in one of the instrument card slots (slots 1 - 12).

When ordered alone, the card's shipping dimensions are:

254 mm x 254 mm x 127 mm. (10 in x 10 in x 5 in).

Weight: 0.34 kg. (0.74 lb).

With Option 01: 0.42 kg. (0.93 lb.)

Weight, Shipping: When ordered with a 53/63 card cage, this card will be installed

and secured in one of the function card slots.

When ordered alone, the card's shipping weight is:

0.8 kg. (1.64 lb).

With Option 01: 0.92 kg. (1.83 lb.)

Mounting Position: Any orientation.

Mounting Location: Installs in any function-card slot of the 53/63 Series Card Cage.

Front Edge Signal

<u>Connector</u>: 1 - 76 pin connector.

Refer to Appendix B for connector pinouts.

Equipment Supplied: 1 - 53A-412 Card.

- Spare fuse (Part # 42202-52001)

1 - Operating Manual (Part # 00000-14120).

1 - Service Manual (Part # 00000-24120).

Optional Equipment: Option 01: Optical Isolation.

Option 02: Open collector I/O.

See Appendix D for a description of the options.

# **OPERATION**

# Overview

The 53A-412 Card is programmed by ASCII characters issued from the system controller to the 53/63 System's communications card. The 53A-412 Card is interfaced to the communications card through the 53 Series or 63 Series Card Cage's backplane.

To address a function card for the first time, the system command @XY must be issued. X is the card cage address (0-9) selected on the 53A-171 Control Card in the addressed card cage; Y is the 53A-412 Card's address (0-9) within the addressed card cage. The 53A-412 Card's address is selected using the card's Address Select switch. Once a function card is addressed, it remains addressed until the system receives another @ character. Appendix A fully discusses the @XY command and the other 53/63 Series system commands. After the 53A-412 Card is addressed, the commands listed below may be issued until another function card is addressed.

# Command Protocol And Syntax

Command protocol and syntax for the 53A-412 Card is as follows:

- 1) A command string consists of a string of ASCII encoded characters (up to 1024 maximum) terminated by a line feed <LF>. Multiple commands may be entered within a string, with a semi-colon used as a delimiter between individual commands.

- 2) Valid command delimiters for the card are the line feed <LF> and the semi-colon (;). The command string is buffered up until a <LF> is encountered, at which time the entire string is evaluated.

- If no delimiter is entered, then the card interprets the next command as being part of the previous command. This causes either an error or an improper setup if the subsequent command is interpreted as part of the previous command.

- 3) All commands are operated on in the order they are received, and executed when the <LF> delimiter is received.

- 4) If a given parameter is omitted within a command, either its default state or its last programmed state will be in effect (depending on the particular command issued).

- 5) Any character may be sent in either upper or lower case form.

- Any command syntax or programming errors will cause the command to be ignored, and an error will be flagged. All commands up to the occurrence of the error will remain valid. The invalid command and all subsequent commands will be lost, and no commands will be accepted until the error condition is cleared, either through a hardware or software reset, or by reading the error out with the Q command. If an error is queued, the card will respond with 'ERROR' until the condition is cleared.

- 7) All responses from the card are terminated by a carriage return and line feed <CR><LF>.

8) The table below shows the valid ASCII character set for the 53A-412. All other characters are treated as white space characters, and are ignored if received.

| Character | ASCII Code (hex) |  |  |  |  |

|-----------|------------------|--|--|--|--|

| <lf></lf> | 0A (line feed)   |  |  |  |  |

| #         | 23               |  |  |  |  |

| &         | 26               |  |  |  |  |

| *         | 2 <b>A</b>       |  |  |  |  |

| +         | 2 <b>B</b>       |  |  |  |  |

| •         | 2 <b>D</b>       |  |  |  |  |

| •         | 2E               |  |  |  |  |

| /         | 2F               |  |  |  |  |

| '0' — '9' | 30 - 39          |  |  |  |  |

| ;         | 3B               |  |  |  |  |

| 'A' - 'Z' | 41 - 5A          |  |  |  |  |

| 'a' - 'z' | 61 - 7A          |  |  |  |  |

# Command Summary

Detailed descriptions of each command (in alphabetical order) are given following the summary. An overview of the commands is as follows:

- I The Input Data command specifies which bytes are to be read, the order in which they are to be read (and reported), and any masks to be overlaid onto the data prior to reporting it. ASCII hex data representing all input bytes, selected input and/or output bytes, or selected bits of a byte (by using a mask) can be returned to the system controller using this command.

- L The Load Output command specifies the data to be output, the order of output, and any masks to be overlaid onto the data prior to output. The ASCII hex data representing all output bytes, selected output bytes, single bits of a byte, or mask overlays onto the byte(s) can be used to update the cards' output data latches.

- M The Mode command defines which bytes are inputs and which are outputs, and their active logic sense (active high true or active low true).

- N These commands set up and control buffered binary input and output.

- O The Operational Setup command returns information on the current setup of the card.

- P The Strobe Pulse Sense command specifies the active edge of the handshake signals (positive or negative edge triggered).

- Q The Query Status command is used to read the current state of the card. The information which can be obtained includes:

- error data;

- the state of the external handshake lines (DRD,RFD);

- the current tri-state condition of the I/O latches;

- the programmed active edges of the handshake signals, and whether the handshake(s) are active;

- the amount of data queued in the output binary buffer;

- the amount of data queued in the input binary buffer;

- the current thread sequence and its state.

- R The Reset command resets the board to its power-up state.

- S The Self Test command causes the card to execute a self test, and then return to its power-up state.

- The Tri-state Control command specifies whether the output bytes are tri-stated (high-impedance), or active. This command is logically OR'ed with the external tri-state lines.

- U The Update command specifies the conditions for which the inputs and outputs are updated (update on command, update on external handshake control, update on time), and for update on time, specifies the timing interval.

- V The Version command returns the current software revision level of the board.

- X The X command is used to enable or disable the interrupt to the system controller. This interrupt can be programmed to be active when either external handshake is valid (DRD, RFD), when the binary input buffer is full, or when the binary output buffer is empty or a breakpoint occurs.

- Z The Tri-state Level command specifies the active level of the external tri-state control lines ETS0-ETS5 (active high true or active low true).

A detailed description of each command, in the same order as listed above, is given on the following pages. The syntax used in the command descriptions is:

- () optional parameter

- { } group of parameters

- '' ASCII character

- ... optional repetition

NOTE: The (), {}, '', and ... characters are not part of the command.

# Command Descriptions

#### Command

#### Description

I or IO

The I (Input) command specifies the data to be input, the order in which it is be input, and any masks which are to be overlaid onto the data prior to reporting it.

The IO (Input Override) command provides the capability to read a different input sequence one time, without destroying the last defined I command input sequence.

Syntax:  $I\{b(o)(d)(/)\}...$  $IO\{b(o)(d)(/)\}...$

- I input command

- IO input override

- b one to six digits which specify the byte number, 0 through 5, or \* for all bytes.

- o one of the following:

- & AND the data specified by (d) to the specified input byte(s).

- # OR the data specified by (d) to the specified input byte(s).

- X XOR the data specified by (d) to the specified input byte(s).

- d ASCII mask value 00 through FF (required with o)

- / an optional character which is allowed to make the command more readable.

Default: I\* (input all bytes)

The bytes can be programmed in any order, and once programmed, the setup remains valid unless specifically redefined by another I command, or by a Reset or Self Test command. Input can be requested for both input and output bytes.

Typical use of the I command simply defines a sequence of bytes to be read, with the sequence defined by the order of the digits following the I command. For example, '1123' specifies that the data from bytes 1, 2, and 3 are to be reported in the order of byte 1 first, byte 2 second, and byte 3 third (followed by <CR><LF>).

Additional input of the same sequence does not require redefining the I command. Successive reads from the card will return new data in the defined sequence, each terminated by <CR><LF>.

For example, '1321' specifies an input sequence of 3-2-1. If bytes 1, 2, and 3 contained 10, 22, and 43 hex, the card would report '432210<CR><LF>' when read. Subsequent reads of the card will report the update state of bytes 3, 2, and 1.

A \* in the I command automatically defines the byte sequence to be 0-1-2-3-4-5.

Each time an I command is issued, it defines a new input sequence. The input override command (IO) is used to look at a specific byte(s) without affecting the I command's sequence, as shown in the example below. Once the I command has been issued, its setup and sequence (including masks) remain valid until overridden by another I command, reset, or self test.

If external Data Ready Strobe has been defined as the condition to latch input data into the card, and no strobe has been received since the last input request, an 'N<CR><LF>' will be returned for both the I and IO commands, indicating no new data is available.

The state of the data returned represents the logic sense programmed with the mode (M) command.

If an I command is issued with no arguments ((b) is omitted), the sequence will be cleared and the card will respond with a <CR><LF> only. If (o) and (d) are omitted, the command specifies data in its raw input form. If (o) is specified without (d), an error will be generated. If any error is queued, the card will respond with ERROR<CR><LF> on the subsequent input requests.

NOTE: All responses from the I and IO commands are terminated in <CR><LF>.

# Example:

The example cases on the following page show how a sequence of I commands and implicit inputs will be reported (each case assumes the I/O lines are at 00, 11, 22, 33, 44, and 55 for bytes 0 to 5 respectively).

| Cas  | e Command                                  | Byte<br>Sequence | Card Response                   |  |  |  |  |  |

|------|--------------------------------------------|------------------|---------------------------------|--|--|--|--|--|

| Setu | Setup M*0;T*I;L*;001122334455;I* <lf></lf> |                  |                                 |  |  |  |  |  |

| 1    | Initial State                              | 0-1-2-3-4-5      | 001122334455 <cr><lf></lf></cr> |  |  |  |  |  |

| 2    | I123 <lf></lf>                             | 1-2-3            | 112233 <cr><lf></lf></cr>       |  |  |  |  |  |

| 3    | read (no I command)                        | 1-2-3            | 112233 <cr><lf></lf></cr>       |  |  |  |  |  |

| 4    | I*&55 <cr><lf></lf></cr>                   | 0-1-2-3-4-5      | 001100114455 <cr><lf></lf></cr> |  |  |  |  |  |

| 5    | read (no I command)                        | 0-1-2-3-4-5      | 001100114455 <cr><lf></lf></cr> |  |  |  |  |  |

| 6    | I* <lf></lf>                               | 0-1-2-3-4-5      | 001122334455 <cr><lf></lf></cr> |  |  |  |  |  |

| 7    | IO3X11 <lf></lf>                           | 3                | 22 <cr><lf></lf></cr>           |  |  |  |  |  |

| 8    | read (no I command)                        | 0-1-2-3-4-5      | 001122334455 <cr><lf></lf></cr> |  |  |  |  |  |

| 9    | I543012 <lf></lf>                          | 5-4-3-0-1-2      | 554433001122 <cr><lf></lf></cr> |  |  |  |  |  |

| 10   | I0#55/1XAA/2345 <lf></lf>                  | 0-1-2-3-4-5      | 55BB22334455 <cr><lf></lf></cr> |  |  |  |  |  |

Setup sets all bytes to outputs (M command); un-tri-states them (T command); defines the load sequence as 0-1-2-3-4-5 (L command); loads the specified data; and inputs all the data in the 0-1-2-3-4-5 sequence (I command).

Case 1 is the initial setup condition.

Case 2 requests the input from bytes 1, 2, and 3 in that order.

Case 3 reports the data from the input sequence set up in case 2.

Case 4 masks (ANDs) each input byte with a 55 hex prior to reporting it. Note that the <CR> character is treated as a white space and is ignored.

Case 5 reports the data using the sequence and mask set up in case 4.

Case 6 overrides the mask from case 4 and reports the data in its raw form.

Case 7 uses the override command to look at byte 3 XOR'd with an 11 hex.

Case 8 reports the data from the sequence defined in Case 6.

Case 9 reports the data in the newly defined sequence 543012.

Case 10 reports the data in the newly defined sequence 012345, ORs byte 0 with a 55 hex, XORs byte 1 with an AA hex, and reports bytes 2, 3, 4, and 5 in their raw form. The optional / is used to make the command more readable.

# Command

# Description

L or LO

The L (Load Output) command specifies the data bytes to be output, the sequence in which it is be output, and any masks which are to be overlaid onto the data prior to output by the card.

The LO (Load Override) command provides the capability to output a different sequence of bytes one time, without destroying the last defined L command output sequence.

Syntax:  $L\{b(o)(d)(/)\}...$  $LO\{b(o)(d)(/)\}...$

- L load output command

- LO load override

- b one to six digits which specify the byte number, 0 through 5, or \* for all bytes. A \* automatically defines the sequence 0-1-2-3-4-5.

- o one or more of the following letters which specify various parameters as follows:

- D Load the data specified by (d) to the specified output byte(s).

- S Set the bit indicated by (d) to a logic high (the eight bits of a byte are defined as 00 through 07, with bit 00 being the least significant bit).

- R Reset the bit indicated by (d) to a logic low (the eight bits of a byte are defined as 00 through 07, with bit 00 being the least significant bit).

- & AND the data specified by (d) to the specified output byte(s).

- # OR the data specified by (d) to the specified output byte(s).

- X XOR the data specified by (d) to the specified output byte(s).

- d ASCII value 00 through FF (required with o). Note that d is an 8-bit wide byte value if the o parameter is a D, &, #, or X, and a bit number if the o parameter is an S or R.

- / optional character allowed to make the command more readable.

Default: NONE [all bytes are initially defined as inputs (M command), set to TTL logic 0, and tri-stated (T command)].

The bytes can be programmed in any order, and once programmed, the setup remains valid unless specifically overridden by another L command, by redefining the I/O configuration (M command), or by a reset or self test command. If any bytes are not programmed, they will remain in their default (or previously programmed) state. The Set, Reset, and Mask parameters (S, R, X, #, and &) all operate on the last data output to a byte(s), and are valid only for the current command.

Typical use of the L command specifies an output byte and the data to be output. For example, 'L2D55' specifies that a 55 hex is to be output to byte 2.

Once an output sequence has been defined with the L command, ASCII hex data (00 - FF) may be written to the card without additional L commands.

The order in which the outputs were specified in the last Load command defines an output sequence. For example, 'L321D55' specifies that a 55 is to be output to bytes 3, 2, and 1. This command also defines the output sequence to be bytes 3-2-1. ASCII hex data sent to the card will then be buffered until the amount of data received matches the amount required by the output sequence. All bytes are thus physically updated at the same time when the total amount of data is received. In this example, six ASCII hex bytes are required since two bytes are required for each output byte. If '123456' were then sent to the card, byte 3 would be loaded with 12, byte 2 with 34, and byte 1 with 56, to match the 3-2-1 sequence. If an L command had not been previously issued, this data would be ignored.

Each time an L command is issued, it defines a new output sequence. The Load Override (LO) command is used to change specific data without affecting the L command's sequence, as shown in the examples below. Note that whenever a new L command is issued, any buffered data in an incompleted buffer is lost. The output sequence is also cleared whenever a new Mode (M) command is issued.

Note that a particular byte should only be defined once within the L command, because it can appear only once in the sequence. If a byte is defined more than once within the command, only the last specified action is taken. For example, 'L0D55/0D44' would load a 44 hex into byte 0 (the load 55 hex action is ignored). Similarly, 'L0S01/0S03' would only set bit 3 of byte 0. Setting both bits can be accomplished by using the mask command 'L0#0A'.

The byte(s) will be physically output based on the conditions defined by the U command.

If output is commanded to a byte which is defined as an input (M command), an error will be flagged, and the command ignored. If the (b) parameter is omitted, the load sequence will be cleared and the card will respond with a <CR><LF> only. The (o) and (d) parameters are optional. However, if (o) is specified without (d), an error will be generated. If an invalid parameter is specified, an error will be generated.

Note that when using the RFD external handshake, the most recent data received by the card is always the next to be output. If two L commands, or two full buffers of data are received before a strobe occurs, the first data will be lost, and the most recent data will be output. To prevent this overwriting of data, read the state of Ready For Data (RFD) with the QR command (see Query Status command) before sending additional data to the card. If the data reported back by the QR command is a 0, then the last data output has not yet been

accepted by the external device. If a 1 is reported back, then the outputs can be updated with no loss of data.

Example:

The following examples show how a sequence of L commands and data will be output.

|      |                                                | Byte                                 | -  |    |    | tes (he | ex)<br>4 | 5  |

|------|------------------------------------------------|--------------------------------------|----|----|----|---------|----------|----|

| Case | Command                                        | Sequence                             | 0  | 1  | 2  | 3       | 4        | 3  |

| 1    | Power-up (default)                             | none                                 |    |    |    |         |          |    |

| 2    | M*O;T*I;I* <lf></lf>                           | N/A                                  | 00 | 00 | 00 | 00      | 00       | 00 |

| 3    | L*D55 <cr><lf></lf></cr>                       | 0-1-2-3-4-5                          | 55 | 55 | 55 | 55      | 55       | 55 |

| 4    | 001122334455                                   | 0-1-2-3-4-5                          | 00 | 11 | 22 | 33      | 44       | 55 |

| 5    | L1D0150DFA2D204D883D6<br>L1D01/50DFA/2D20/4D88 |                                      | FA | 01 | 20 | CC      | 88       | FA |

| 6    | 001122334455                                   | 1-5-0-2-4-3                          | 22 | 00 | 33 | 55      | 44       | 11 |

| 7    | LO1S04 <lf></lf>                               | no change                            | 22 | 10 | 33 | 55      | 44       | 11 |

| 8    | L123#80 <cr><lf></lf></cr>                     | 1-2-3                                | 22 | 90 | В3 | D5      | 44       | 11 |

| 9    | 001122                                         | 1-2-3                                | 22 | 00 | 11 | 22      | 44       | 11 |

| 10   | L150243 <lf></lf>                              | 1-5-0-2-4-3                          | 22 | 00 | 11 | 22      | 44       | 11 |

| 11   | 001122334455                                   | 1-5-0-2-4-3                          | 22 | 00 | 33 | 55      | 44       | 11 |

| 12   | L*D33 <lf></lf>                                | 0-1-2-3-4-5                          | 33 | 33 | 33 | 33      | 33       | 33 |

| 13   | L0S02/1R04/2&22/3X22/4                         | #44 <cr><lf><br/>0-1-2-3-4</lf></cr> | 37 | 23 | 22 | 11      | 77       | 33 |

| 14   | 0011                                           |                                      | 37 | 23 | 22 | 11      | 77       | 33 |

| 15   | 223344                                         |                                      | 00 | 11 | 22 | 33      | 44       | 33 |

| 16   | LO41D55 <lf></lf>                              |                                      | 00 | 55 | 22 | 33      | 55       | 33 |

| 17   | AABBCCDDEE                                     |                                      | AA | вв | CC | DD      | EE       | 33 |

Case 1 is the initial state of the outputs. All outputs are in a tri-state condition.

Case 2 defines all bytes as outputs and un-tri-states them. The I\* command at the end of the line can be used to read back the output data and verify that it is all 0s, if an input request is issued following this command.

- Case 3 loads all outputs with 55 hex, with the \* defining the sequence as 012345.

- Case 4 is data received from the system controller. The data is output in the order it is received according to the current sequence.

- Case 5 loads each byte individually, and redefines the sequence to be 150243. The line below case 5 shows the same command using the optional / character.

- Case 6 is more data, again output in the order it is received, according to the current sequence.

- Case 7 uses the load override command to force bit 4 of byte 1 high without changing the sequence.

- Case 8 OR's the current data of bytes 1, 2, and 3 with an 80 hex, and redefines the output sequence to 123.

- Case 9 loads new data into bytes 1, 2, and 3.

- Case 10 redefines the output sequence without affecting the data.

- Case 11 loads data for the newly defined sequence.

- Case 12 loads all bytes with 33 hex.

- Case 13 sets bit 2 of byte 0, resets bit 4 of byte 1, AND's byte 2 with hex 22, XOR's byte 3 with hex 22, and OR's byte 4 with a hex 44.

- Case 14 has no effect on the outputs because not enough data has been received based on the last sequence defined (01234).

- Case 15 supplies the rest of the data needed for the sequence, and the new data is output.

- Case 16 uses the override command to force bytes 4 and 1 to a hex 55.

- Case 17 outputs new data based on the sequence from case 13, which is still in effect.

Note that each time a Load command is received, a new sequence is defined for any subsequent data, and that the Load Override command does not affect the output sequence.

# Command

M

The M (Mode) command defines which bytes are inputs and which are outputs, and their active sense.

Syntax:  $M \{(b)(m)(1)\}...$

Description

- b byte number, 0 through 5, or \* for all bytes.

- m I or O, Input or Output respectively

- 1 H or L, Logic state, High or Low true respectively.

Default: M\*IH (all inputs, active high true)

The bytes can be programmed in any order, and once programmed, the setup remains valid unless specifically overridden by another M command, or by a Reset or Self Test command. If any bytes are not programmed, they will remain in their default (or previously programmed) state.

If (m) or (l) is omitted, the default (or previously programmed state) will be used for the omitted parameter of the byte(s) being programmed. If (b) is omitted, the command will have no effect. If an invalid parameter is sent, an error will be generated.

If the logic state is programmed as active high true, then a 1 on an input or output command reflects a TTL logic 1 on the I/O pin. If the logic state is programmed as active low true, then a 1 on an input or output command reflects a TTL logic 0 on the I/O pin.

*NOTE*:

The Mode command automatically resets the sequence set up by the L (Load) command to 'null', and clears any pending RFD handshakes.

#### Example:

The following examples show how a sequence of mode commands will affect the configuration setup of the card:

| 9 | <u>Case</u> | Command                  | Byte     | e I/O | and S    | ense (   | H or I   | <u>-)</u> |

|---|-------------|--------------------------|----------|-------|----------|----------|----------|-----------|

|   |             |                          | <u>Q</u> | 1     | <u>2</u> | <u>3</u> | <u>4</u> | <u>5</u>  |

|   | 1           | Power-up (default)       | I/H      | I/H   | I/H      | I/H      | I/H      | I/H       |

|   |             | M3O <lf></lf>            | I/H      | I/H   | I/H      | O/H      | I/H      | I/H       |

|   | 3           | M105L <cr><lf></lf></cr> |          | I/L   |          |          |          |           |

|   | 4           | M012OH345IL <lf></lf>    | O/H      | O/H   | O/H      | I/L      | I/L      | I/L       |

|   |             | M*OL <cr><lf></lf></cr>  |          | O/L   |          |          |          |           |

|   |             | M23I*H <lf></lf>         |          | O/H   |          |          |          |           |

- Case 1 is the power-up default state.

- Case 2 sets up byte 3 as an output. Since the logic sense was not specified, it remains in its previously programmed (default) state of active high.

- Case 3 sets up bytes 1, 0, and 5 as active low. All other bytes remain in their previously programmed state. A <LF> is used to delimit this command with the <CR> being ignored.

- Case 4 sets up bytes 0, 1, and 2 as outputs, active high, and bytes 3, 4, and 5 as inputs, active low.

- Case 5 sets all bytes to outputs, active low.

- Case 6 sets up bytes 2 and 3 as inputs, and all bytes as active high.

# Command

# Description

N

The N commands are used to set up and control binary input and output.

For binary input, the commands are:

- NIA allocates the size of the binary input buffer and the binary input mode.

- NIT enables the binary input

- NIX transfers binary data from the card

- NID disables the binary input mode

# related commands:

- M (mode) define which bytes are inputs and outputs

- I (input) define the input data sequence

- UD (update) update the input on the data ready handshake

- QB (query) returns the number of bytes queued in the input buffer

- XAB (interrupt) generates an interrupt when the input buffer is full

For binary output, the commands are:

- NOA allocates the size of the binary output buffer and the binary output mode.

- NOX preloads/loads binary data into the output buffer

- NOS defines a threading sequence for output mode 2

- NOC continues the thread sequence after a breakpoint for output mode 2

- NOR redefines part or all of a thread for output mode 2

- NOT enables the binary output

- NOD disables the binary output mode

### related commands:

- M (mode) define which bytes are inputs and outputs

- L (load) define the output data sequence

- U (update) define the update condition as the ready for data interrupt or the programmable timers.

- QO (query) returns the number of bytes still in the output buffer that have not yet been transmitted (output mode 1)

- QK returns the current thread sequence in effect and its break condition (output mode 2)

- XAO generates an interrupt when the output buffer is empty (output mode 1), or when a breakpoint occurs (output mode 2)

A detailed description of each of the N commands follows.

NIA / NOA Allocate Binary Buffer Memory.

The NIA and NOA commands are used to set up and allocate binary input and output buffers respectively, and to define the binary mode.

Syntax: NIA[x]M[y] Allocate the binary input buffer memory NOA[x]M[y] Allocate the binary output buffer memory

- [x] amount of memory allocated; 0 to 6000 max.

- [y] 1 or 2, the binary mode

A total of 6000 bytes is available for the input and output binary buffers. This memory can be split between the two buffers in any proportion. For example, if 4000 bytes were allocated to the output buffer, up to 2000 bytes could be allocated to the input buffer.

For an NOA command, the amount of memory allocated should be an integer multiple of the number of bytes defined as outputs (Load (L) command). For an NIA command, the amount of memory allocated should be an integer multiple of the amount of bytes defined as inputs (Input (I) command). For example, if 3 bytes were defined as outputs, and it is desired to output data 100 times, then (3 \* 100) = 300 bytes should be allocated to the output buffer. Similarly, if 2 bytes were defined as inputs, and it is desired to input data 2500 times, then (2 \* 2500) = 5000 bytes should be allocated to the input buffer.

Issuing an NOA or NIA command will reset the associated buffer addresses and counters to 0. If the total memory allocated to the two buffer exceeds 6000, then an error will be generated. The NOA or NIA command must be issued once before any other N output or input command, respectively.

# Binary Input Modes

Binary input can only be used in conjunction with the data ready (DRD) handshake (see the Update (U) command). Two modes are provided for buffered binary input. Mode 1 (e.g NIA100M1) inputs data as long as there is free memory in the buffer to accept it. For mode 1, if a DRD handshake had occurred when the memory was full, the handshake will be queued until enough memory to input another sequence is freed. When the memory is freed, the data will be input and the handshake acknowledged.

Mode 2 (e.g NIA100M2) will overwrite the oldest data in memory if the input buffer is full. If the mode is improperly specified, an error will be generated. By using the NIX command, data can be simultaneously read from the input buffer while new data is being strobed in. This in effect dynamically frees up memory for additional input.

The number of bytes queued up in the input buffer can be read at any time by using the QB query command. Also, the X command can be used to generate an interrupt when the input buffer is full.

# Binary Output Modes

Binary output can be used in conjunction with the ready for data (RFD) handshake, or the programmable timers (see the Update U command). Two modes are provided for buffered binary output. Mode 1 (e.g. NOA100M1) outputs data as long as there is enough data loaded in memory for another output sequence. For mode 1, if a RFD handshake had occurred when the memory was empty, the handshake will be queued until enough data has been loaded to output another sequence. The new data will then be output and the handshake acknowledged.

Mode 2 (e.g. NOA100M2) outputs the data based on a programmed thread sequence (NOS command). If the mode is improperly specified, an error will be generated. By using the NOX command, data can be simultaneously loaded into the output buffer while data is being output to the front end.

For mode 1, the number of bytes left to be output can be read at any time by using the QO query command. For mode 2, the QK command can be used to determine the current sequence and its state. Also, the X command can be used to generate an interrupt when the output buffer is empty for mode 1, or when a breakpoint occurs for mode 2.

\*\*\*\*\*\*\*

NID / NOD

Disabling Binary I/O

The NOD and NID commands are used to disable binary outputs or inputs respectively.

Syntax:

NID NOD Disable the input binary transfers

Disable the output binary transfers

\*\*\*\*\*\*\*

NIX / NOX

Binary Data Transfer

The NIX and NOX commands are used respectively to read binary data from the card or to load binary data into the card.

Syntax:

NIX[x]/[y] Transfer binary data from the card.

NOX[x]/[y] Transfer binary data to the card.

- [x] amount of binary data to transfer, 0 to the allocated buffer size

- [y] optional parameter specifying a specific buffer location

If [x] or [y] is less than zero or greater than the respective allocated buffer size, an error will be generated.

# Loading Binary Output Data

For the NOX command, the card will go into the binary input mode to accept binary data from the backplane. The card will stay in binary until either the specified amount of data has been loaded, or the card is read from. The data will be loaded and output based on the current output sequence as defined by the Load command. For example, if three bytes were defined as outputs and output sequence was 5-4-0 (L540), then the first byte loaded would correspond to latch 5, the second to latch 4, the third to latch 0, the fourth to latch 5, the fifth to latch 4, etc. [y] is an optional parameter which specifies where the data is to be loaded in the output buffer.

NOTE: The [y] option is primarily intended for preloading the output data. To prevent erroneous operation, do not use it if the card is actively outputting data.

If [y] is specified, the data will be loaded beginning at the address specified by [y]. For example, an NOX1000/0 command would load the subsequent downloaded binary data into the output buffer beginning at address 0 (the first location) of the binary output buffer. To load an additional 1000 bytes, issuing either an NOX1000 or NOX1000/1000 would then load the data into the next 1000 locations. The card automatically wraps around to the beginning of the buffer when the end of the buffer is reached. Note that the NOA command automatically sets the starting address to 0.

For output mode 1, once the data has been initially loaded into the card and the binary output enabled (NOT command), the NOX command can be used to dynamically load additional data into the output buffer as memory is freed. A QO command should first be executed to verify there is enough free memory in the buffer to download the additional data (to prevent erroneous operation by possibly overwriting data which has not yet been output). After receipt of the NOX command the data will be loaded into the buffer following the data still queued to be output. For example, if 30 bytes were still left to be output and an NOX1000 command were issued, the new downloaded binary data would be loaded immediately following the location of the 30th data byte. As each byte is transferred, the counter (QO) response is automatically incremented to reflect the additional amount of data loaded into the card.

For output mode 2, the NOX command can be used to download the individual threads into specific locations in memory. After the data has been loaded and the thread sequence defined (NOS command), the NOT command can be used to begin the output.

If extreme caution is used, new data can be loaded into the card to dynamically change a data thread. To do this, either the thread should be at a breakpoint, or the new data loaded should be loaded into allocated but unused output buffer memory. For either of these cases, the new data can be loaded without the chance of overwriting the data of an active thread. Also, the NOR command can be used to redefine

the threading sequence if desired at this point. The NOC command is used to restart the sequence after a breakpoint. The QK command can be used to determine the current sequence in effect and its state (executing or at a breakpoint).

# Reading Binary Input Data

For the NIX command, the card will go into the binary input mode to transfer binary data from the input buffer to the backplane. The card will stay in binary mode until either the specified amount of data has been transferred, or the card is written to. The QB command can be used to determine how much data is queued up in the input buffer. The NIX command automatically outputs data beginning from the oldest data in memory. It can be used to dynamically transfer data from the card (thus freeing up memory for more input) while data is actively being input into the card.

For example, if 100 input bytes were queued, issuing an NIX50 would return the oldest 50 bytes in memory (virtual locations -100 to - 51). Issuing another NIX50 command would then return the next 50 bytes (virtual locations -50 to -1). As each byte is transferred, the QB response is automatically decremented by one to indicate the new amount of data queued in the input buffer. The data is reported based on the input sequence as defined by the input (I) command. For example, if three bytes were defined as inputs, and the input sequence was 3-2-1 (I321), then the first byte returned would correspond to input latch 3, the second to input latch 2, the third to input latch 1, the fourth to input latch 3, etc. The card automatically wraps around to the beginning of the buffer when the end of the buffer is reached.

[y] is an optional parameter which specifies where in the input buffer data is to be transferred from. If [y] is specified, it should be an integer multiple of the number of bytes defined by the input (I) command to prevent skewing of the reported data relative to the input sequence.

NOTE: The [y] option is primarily intended for post-processing of the input data (NID issued to stop the input). To prevent erroneous operation, do not use it if the card is actively inputting data.

[y] is referenced to the address of the next byte to be input, which is virtual address 0. If [y] is specified, the data is transferred beginning at the address specified by [y]. For example, issuing an NIX1/1 will transfer the most recent byte input by the card. Similarly, an NIX100/100 will transfer the most recent 100 bytes input by the card. As each byte is transferred, the QB response data is decremented by one. Note that the NIA command automatically sets the starting virtual address to physical address 0 of the input buffer.

\*\*\*\*\*\*

# NOS Defining A Thread Sequence For Output Mode 2

A thread is sequential data beginning at a specified address, and of a specified size. For example, one thread could begin at the output buffer address 100 and stretch 10 bytes. Another thread could begin at address 9 and stretch 18 bytes. The data in the threads is loaded by the NOX command. By defining a thread sequence with the NOS command, very specific data patterns and control can be effected on the output data. Up to 50 threads can be defined with the NOS command.

Syntax: NOS([w]/[x]/[y][z])...

- [w] the starting address of the thread

- [x] the number of data outputs

- [z] the number of times to repeat this thread

- [z] either B or C:

- B = break after completing this thread

- C = continue to the next thread after completing this one

- [w] the starting address of the thread, and the physical location of the output data buffer where the thread is to begin.

- [x] the number of data outputs for the current thread. Note that the actual number of bytes to be output will be the number of bytes defined as outputs by the load (L) command times [x]. For example, if 3 bytes were defined as outputs, and [x] were 10, then 30 contiguous bytes in memory would be required for the thread.

- [y] the number of times to repeat the current thread. Using the above example, if [y] were defined as 2, then a total of 60 bytes would be output (3 \* [x] \* [y]). Since three bytes are output per handshake (or timer tick), a total of 20 handshakes (or ticks) would be required to output the thread.

- [z] the action to be taken when the current thread is completed. If [z] = B, then output will be suspended (or broken) when the thread is complete. At this point, new thread data could be loaded with the NOX command, and/or the thread sequence could be modified using the NOR command. if [z] = C, then the data will continue to the next thread in the sequence. The first thread defined is thread 0, the next thread 1, etc. When the end of the threading sequence is complete, the sequence will automatically restart back to thread 0 if the last thread is programmed to continue to the next thread.

Issuing an NOS command automatically puts the card into output mode 2. The NOS command is used to define the threads for output mode 2 and will have no effect if specified in output mode 1.

If an RFD handshake occurs when a breakpoint is active, the handshake will be queued, and the next data output when the breakpoint is deactivated with an NOC command. If [w] or [x] is less than zero or greater than the allocated buffer size, an error will be generated. If [y] is less than zero or greater than 32767, an error will be generated. If the number of sequences defined is greater than 50, an error will be generated. Also, if any parameter is missing or improperly specified, an error will be generated.

To illustrate the threading operation, assume that byte 0 only has been defined as an output (L0), and that 10 sequential binary bytes beginning with 0 have been loaded into the output buffer at address 0 (NOX10/0 command). If the threading sequence were defined as NOS 0/5/1C 7/2/2C 3/3/1B then the data that would be output would be 0-1-2-3-4-7-8-3-4-5. Note that the spaces in the NOS are white space characters and ignored by the card. If the sequence were restarted with an NOCB command (continue from break), then the entire sequence would be repeated. If the sequence were again restarted with an NOC1 command (continue from break at sequence 1), then the data that would be output would be 7-8-7-8-3-4-5.

\*\*\*\*\*\*\*\*

NOC

Continuing A Thread From A Breakpoint (Output Mode 2)

The NOC command is used to continue the threading sequence after a breakpoint has occurred in output mode 2, and will be ignored if specified in output mode 1.

Syntax: NOC[x][I]

- [x] B, or an integer value:

- B continue from the current breakpoint to the next thread integer value from 0 to the number of threads defined continue from the breakpoint at the defined thread.

- [I] optional parameter which specifies that the next thread is to be initiated regardless of the state of the RFD handshake.

If an NOCB command were issued, the thread following the one causing the break will be executed. If the thread is the last one in the sequence, it will be set back to the first one (thread 0). The threading can be continued from any point after a breakpoint by specifying which thread to continue from. For example, an NOC5 will continue with the sixth defined thread of the sequence (thread 0 is the first defined thread). The I option of the command is useful when it is necessary to 'bootstrap' the output to get the handshaking process started (e.g. NOCBI or NOC0I commands). If a thread number is defined outside of the total number of threads defined by the NOS command, an error will be generated.

\*\*\*\*\*\*\*

#### NOR Redefine Thread Parameters

The NOR command redefines some or all the parameters of a thread.

Syntax: NOR[n][y][z] redefine a particular parameter of a

thread

NOR[n]A[w]/[x]/[y][z]

redefine all the parameters of a

thi

For specific parameters:

- [n] the thread number

- [y] one of the following letters:

- S redefine the starting address of the thread

- D redefine the number of data outputs

- N redefine the number of times to repeat the current this thread

- B break after completing this thread

- C continue to the next thread after completing this one

- [z] the new parameter value. [z] should not be issued for [y] = B or C.

The NOR command can be issued at any time once a sequence has been defined by the NOS command. However, caution should be exercised if data is being actively output by the card to prevent changing a sequence which is active. The QK command can be used to read the current active sequence, and its associated state (executing or at a breakpoint). To change the entire threading sequence, issue another NOC command.

If an NOS command of NOS1/2/3C 4/5/6B were issued, the following examples show how the applicable thread would be modified.

| command     | thread 0 | thread 1 |  |  |

|-------------|----------|----------|--|--|

| initial     | 1/2/3c   | 4/5/6b   |  |  |

| nor0s9      | 9/2/3c   | 4/5/6b   |  |  |

| norld8      | 9/2/3c   | 4/8/6b   |  |  |

| nor0n10     | 9/2/10c  | 4/8/6b   |  |  |

| norlc       | 9/2/10c  | 4/8/6c   |  |  |

| nor0b       | 9/2/10b  | 4/8/6c   |  |  |

| nor0a5/4/3c | 5/4/3c   | 4/8/6c   |  |  |

\*\*\*\*\*\*\*\*\*\*\*\*\*

NIT / NOT Enable Binary Input/Output Mode

Syntax: NIT[I] Enable (trigger) the binary input mode

NOT[x][I] Enable (trigger) the binary output mode

- [x] the number of times to output the binary output data or to execute the threading sequence. \* or 0 will output the data continuously until an NOD command is issued to disable the output.

- [I] optional parameter to initiate the binary input or output regardless of the state of the applicable handshake line.

# **Enabling Binary Input**

The NIT command is used to enable binary input. If the card has not been programmed to update on the data ready (DRD) handshake, the command will have no effect. The NIT command sets all buffer pointers to 0, clears any pending DRD handshakes, and clears the data queued counters (QB command).

The I option of the command is useful when it is necessary to 'bootstrap' the input to get the handshaking process started (e.g. NITI). If issued, the card will input the first data sequence regardless of the state of the data ready handshake. This will cause the data acknowledge (DAK) handshake to go active. Once the card has been set up for binary inputs (NIA command), the NIT command can be issued any time to restart binary input. For example, if an NID command were issued to disable binary inputs in order to look at the data, then issuing an NIT command will flush the buffer by clearing the pointers and counters, and re-enable the binary input.

# **Enabling Binary Output**

The NOT command is used to enable binary output. If the card has not been programmed to update on the ready for data (RFD) handshake or the timers, then the command will have no effect. For output mode 1, [x] is the number of bytes that have been preloaded into the buffer (from 0 to the allocated buffer size). Any pending RFD handshakes will be cleared, the buffer starting address will be set to 0, the data queued counter (QO) will be set to the value of [x], and the appropriate update condition will be enabled. If [x] = 0, then the card will wait for data to be loaded (NOX command) before any output will occur.

For output mode 2, the NOT command sets all buffer pointers to 0, resets the QK response and the thread sequence to 0, clears any pending RFD handshakes, and enables the appropriate update condition. [x] is the number of times to repeat the entire thread sequence. The maximum value of [x] is 32767. If [x] is 0, \*, or not specified, the sequence will be repeated indefinitely until either the card is reset or the binary output is disabled with an NOD command.

The I option of the command is useful when it is necessary to bootstrap the output to get the handshaking process started (e.g. NOT1I). If issued, the card will output the first sequence regardless of the state of the ready for data handshake. This will cause the data available (DAV) handshake to go active. Once the card has been set up, the NOT command can be issued at any time to restart the binary output.

#### Command

# Description

0

The O (Operational setup) command returns the operational setup parameters for the card.

Syntax: O

The information returned by the O command reflects the programmed setup of the card. The information is returned in the following format.

\_\_indicates an ASCII space character.

MODE\_[A]\_SENSE\_[B]\_TRI-STATE\_[C]\_TRI-LEVEL\_[D]\_

INPUT\_[E][F]\_OUTPUT\_[G][F]\_DAV[F]\_DAK[F]\_OUT-SEQ[]\_

[H] IN-SEQ[] [H] IN-FUNC [I] IN-MASK\_[J]\_INTR\_[KLMN]

The meaning of each variable is:

[A] = XXXXXX where X = I (Input byte) or O (Output byte). (The rightmost X corresponds to byte 0.)

[B] = XXXXXX where X = H (Logic high true) or L (Logic low true).

(The rightmost X corresponds to byte 0.)

[C] = XXXXXX where X = A (Tri-state active) or I (Tri-state inactive).

(The rightmost X corresponds to byte 0.)

[D] = XXXXX where X = H (External tri-state active high) or L (External tri-state active low).

[E] = CMD Update the input on command.

DRD Update the input on data ready handshake.

[F] = + or - Active edge of the handshake (meaningless for CMD updates).

[G] = CMD Update the output on command.

RFD Update the output on ready for data handshake.

TIME Update the output on time value

[H] = XXXXXX

where X is an ASCII integer; the programmed input/output load sequence is read from left to right. X = - if the sequence is less than 6 bytes.

[I] = XXXXXX

where X indicates the input data mask function. Valid values for X are: & (AND); # (OR); X (exclusive OR); or - (no mask). The leftmost X corresponds to the first byte in the load sequence.

$[J] = XX_XX_XX_XX_XX_XX_XX$

where XX is the ASCII Hex mask value. The leftmost XX corresponds to the mask of the first byte in the load sequence.

[KLMN] interrupt status, where

K = D Data ready interrupt enabled

L = R Ready for data interrupt enabled

M = B Binary input buffer full interrupt enabled

N = O Binary output buffer empty interrupt

enabled; or - Applicable interrupt not enabled

The power-up default operational response of the card is:

MODE IIIIII SENSE HHHHHHH TRI-STATE AAAAAA TRI-LEVEL LLLLLL INPUT CMD+ OUTPUT CMD + DAV+ DAK+ OUT-SEQ[] ------ IN-SEQ[] 012345 IN-FUNC[] ------ IN-MASK[] 00 00 00 00 00 00 INTR ----

P

### Description

The P (Strobe Pulse Sense) command specifies the active edge of the handshake signals.

Syntax:  $P \{(p)...(e)\}$

- p a single character which specifies the strobe pulse to be defined:

- A Data Available Strobe

- R Ready for Data Strobe

- D Data Ready Strobe

- K Data Acknowledge Strobe

- \* All strobes

- e specifies the active edge of the specified strobe as follows:

- + positive edge triggered strobe pulse

- negative edge triggered strobe pulse

Default: P\*+ (all pulse senses positive edge triggered)

The bytes can be programmed in any order, and once programmed, the setup remains valid unless specifically overridden by another P command, or by a Reset or Self Test command. If an edge is not programmed, it will remain in its default (or previously programmed) state. If (e) or (p) is omitted, the command will have no effect. If an invalid parameter is specified, an error will be generated.

This command assumes the U (update) command has specified the use of the handshake signals. If not, this command will have no effect until a U command is issued.

## Example:

The following examples show how a sequence of pulse commands will control the pulse trigger active edges:

|      |                            |          | Pulse E  |          |          |  |

|------|----------------------------|----------|----------|----------|----------|--|

| Case | Command                    | <u>A</u> | <u>R</u> | <u>D</u> | <u>K</u> |  |

| 1    | Power up (default)         | +        | +        | +        | +        |  |

| 2    | PAK- <cr><lf></lf></cr>    | -        | +        | +        | -        |  |

| 3    | P*- <lf></lf>              | -        | •        | -        | -        |  |

| 4    | PKD+ <lf></lf>             | -        | -        | +        | +        |  |

| 5    | PAR+DK- <cr><lf></lf></cr> | +        | +        | -        | -        |  |

Case 1 is the power up (default) condition, which sets all handshake lines as positive edge triggered.

Case 2 sets the DAV and DAK pulses as negative edge true, leaving RFD and DRD in their previously programmed (default) state.

Case 3 sets all handshake lines negative edge triggered.

Case 4 sets the DAK and DRD strobes as positive edge triggered.

Case 5 sets the DAV and RFD strobes as positive edge triggered, and the DRD and DAK strobes as negative edge triggered.

## Description

Q

The Q (Query Status) command returns the status of various hardware and software states.

Syntax: Q(s)

- one of the following letters, which specifies what is to be returned:

- A returns an ASCII error message (see also the N parameter).

- B returns the number of bytes queued in the binary input buffer. The response is formatted as a four-character ASCII integer.

- D returns the state of the external Data Ready Strobe. 0 indicates the handshake has not occurred, and 1 indicates it has.

- returns the programmed state of the interrupts, and which conditions were active at the time the 53A-412's controller last acknowledged an interrupt from the card. The response is formatted as a two character hexadecimal string. Bit 0 represents interrupt on binary output buffer empty (or breakpoint active), bit 1 is binary input buffer full, bit 2 is RFD, and Bit 3 is DRD. A 1 in any of these bit positions indicates the interrupt is enabled, while a 1 in bit positions 4, 5, 6, and 7 indicate respectively which conditions were active when the interrupt was generated. Bit 7 is the most significant bit of the first hexadecimal character. (See the X command.)

- K returns the current thread sequence number and its associated state. The response is formatted as a two-character ASCII integer followed by either 'E' or 'B'. An E indicates the thread is executing, and a B indicates the thread is at a breakpoint.

- N returns an ASCII 00 99 numeric error code. The codes and their messages are listed below.

- O returns the number of bytes queued in the output binary buffer (the number of bytes left to be output). The response is formatted as a four-character ASCII integer.

- R returns the state of the external Ready for Data Strobe. 0 indicates the handshake has not occurred, and 1 indicates it has.

T returns the actual current tri-state condition of each output byte (the OR of each byte's external tri-state control line and its tri-state condition as programmed by the T command). The response is formatted as a two character hexadecimal string (00 - 3F). Bits 0 through 5 represent bytes 0 through 5. For example, bit 0 (01) represents byte 0, bit 5 (20) represents byte 5. A 1 in a bit position indicates the corresponding byte is tri-stated.

For the QR, QD, QB, QK, and QO commands, once the Q command has been issued, subsequent input requests will continuously return the respective information until overridden by another Q command, by an I command, or by reset or self test.

If an error is queued while the I command or any Q command other than QA or QN is the active input request mode, the card will respond with ERROR<CR><LF> until either a QA or QN command is issued to acknowledge the error condition. If (s) is not one of the specified characters, the card will respond with 'READY'.

## Examples:

The following examples show how each of the above commands will respond on power-up:

| Command           | Response                     |

|-------------------|------------------------------|

| read (no command) | READY <cr><lf></lf></cr>     |

| QA <lf></lf>      | NO ERRORS <cr><lf></lf></cr> |

| QB <lf></lf>      | 0000 <cr><lf></lf></cr>      |

| QD <lf></lf>      | 1 <cr><lf></lf></cr>         |

| QI <lf></lf>      | 00 <cr><lf></lf></cr>        |

| QK <lf></lf>      | 00E <cr><lf></lf></cr>       |

| QN <lf></lf>      | 00 <cr><lf></lf></cr>        |

| QO <lf></lf>      | 0000 <cr><lf></lf></cr>      |

| QR <lf></lf>      | 1 <cr><lf></lf></cr>         |

| QT <lf></lf>      | 3F <cr><lf></lf></cr>        |